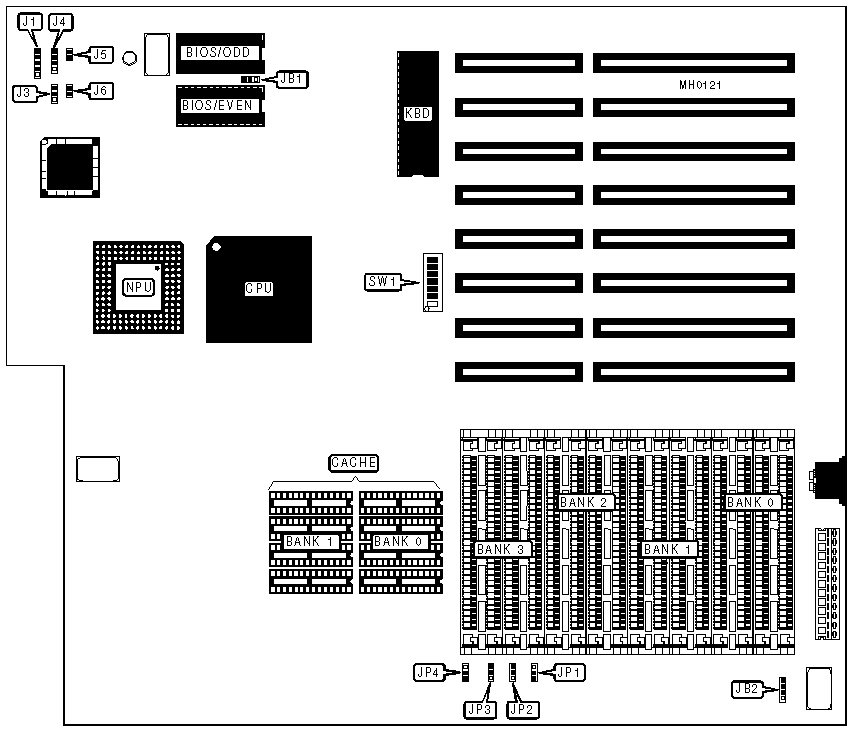

ADVANCED INTEGRATION RESEARCH, INC.

486LC

|

Processor |

80486DX |

|

Processor Speed |

25/33MHz |

|

Chip Set |

UMC |

|

Max. Onboard DRAM |

16MB |

|

Cache |

128/256KB |

|

BIOS |

AMI/Award/Phoenix |

|

Dimensions |

355mm x 304mm |

|

I/O Options |

None |

|

NPU Options |

4167 |

|

CONNECTIONS | |||

|

Purpose |

Location |

Purpose |

Location |

|

Power LED & keylock |

J1 |

Turbo LED |

J6 |

|

Speaker |

J4 |

External 6V battery |

JB2 |

|

Reset switch |

J5 | ||

|

Note:No internal battery is provided, an external battery must be used. | |||

|

USER CONFIGURABLE SETTINGS | |||

|

Function |

Jumper/Switch |

Position | |

| » |

CPU speed select high |

J3 |

pins 1 & 2 closed |

|

CPU speed select low |

J3 |

pins 2 & 3 closed | |

| » |

Factory configured - do not alter |

SW1/1 |

N/A |

| » |

UNIX operating system not installed |

SW1/2 |

Off |

|

UNIX operating system installed |

SW1/2 |

On | |

| » |

External cache memory disabled |

SW1/3 |

Off |

|

External cache memory enabled |

SW1/3 |

On | |

| » |

Memory range 00C00000-00FFFFFF (12-16MB) cacheable |

SW1/4 |

Off |

|

Memory range 00C00000-00FFFFFF (12-16MB) non-cacheable |

SW1/4 |

On | |

| » |

Monitor type select color |

SW1/5 |

On |

|

Monitor type select monochrome |

SW1/5 |

Off | |

| » |

Onboard DRAM enabled |

SW1/6 |

On |

|

Onboard DRAM disabled |

SW1/6 |

Off | |

|

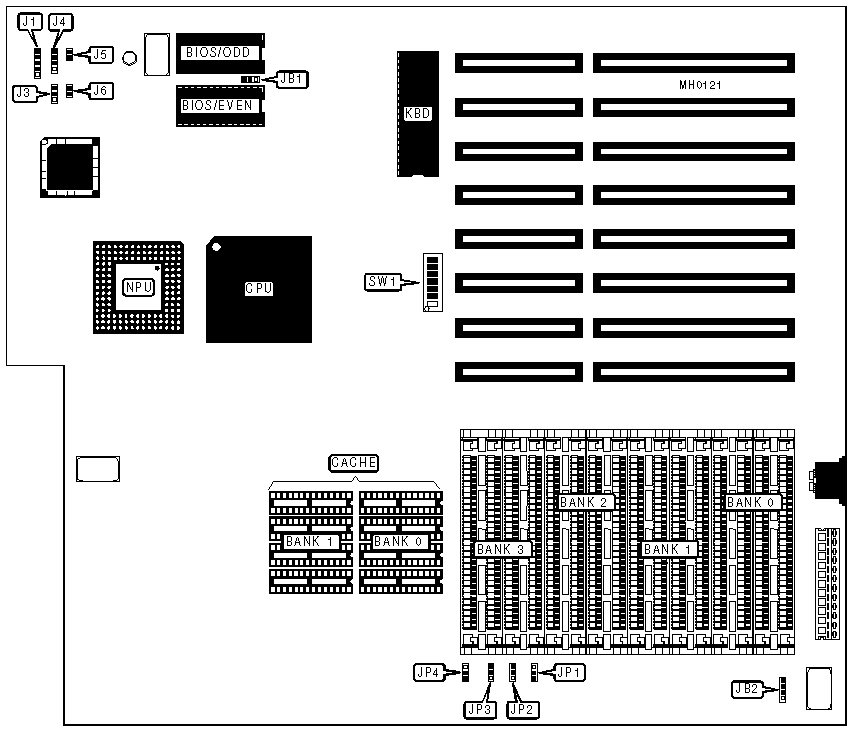

DRAM CONFIGURATION | ||||

|

Size |

Bank 0 |

Bank 1 |

Bank 2 |

Bank 3 |

|

1MB |

(4) 256K x 9 |

NONE |

NONE |

NONE |

|

2MB |

(4) 256K x 9 |

(4) 256K x 9 |

NONE |

NONE |

|

3MB |

(4) 256K x 9 |

(4) 256K x 9 |

(4) 256K x 9 |

NONE |

|

4MB |

(4) 256K x 9 |

(4) 256K x 9 |

(4) 256K x 9 |

(4) 256K x 9 |

|

4MB |

(4) 1M x 9 |

NONE |

NONE |

NONE |

|

8MB |

(4) 1M x 9 |

(4) 1M x 9 |

NONE |

NONE |

|

12MB |

(4) 1M x 9 |

(4) 1M x 9 |

(4) 1M x 9 |

NONE |

|

16MB |

(4) 1M x 9 |

(4) 1M x 9 |

(4) 1M x 9 |

(4) 1M x 9 |

|

DRAM JUMPER CONFIGURATION | |||

|

Size |

JP1 |

JP2 |

JP3 |

|

1MB |

pins 1 & 2 closed |

pins 1 & 2 closed |

pins 1 & 2 closed |

|

2MB |

pins 2 & 3 closed |

pins 1 & 2 closed |

pins 1 & 2 closed |

|

3MB |

pins 1 & 2 closed |

pins 2 & 3 closed |

pins 1 & 2 closed |

|

4MB |

pins 2 & 3 closed |

pins 2 & 3 closed |

pins 1 & 2 closed |

|

4MB |

pins 1 & 2 closed |

pins 1 & 2 closed |

pins 2 & 3 closed |

|

8MB |

pins 2 & 3 closed |

pins 1 & 2 closed |

pins 2 & 3 closed |

|

12MB |

pins 1 & 2 closed |

pins 2 & 3 closed |

pins 2 & 3 closed |

|

16MB |

pins 2 & 3 closed |

pins 2 & 3 closed |

pins 2 & 3 closed |

|

CACHE CONFIGURATION | ||

|

Size |

Bank 0 |

Bank 1 |

|

128KB |

(4) 32K x 8 |

NONE |

|

256KB |

(4) 32K x 8 |

(4) 32K x 8 |

|

Note:Model 486LC may be equipped with 4 DIP sockets for a maximum of 128KB cache. | ||

|

MEMORY CHIP SPEED JUMPER CONFIGURATION | ||

|

25MHz |

33MHz |

JP4 |

|

80ns |

60ns |

pins 1 & 2 closed |

|

100ns |

80ns |

pins 2 & 3 closed |

|

BIOS CONFIGURATION | ||

|

Size |

JB1 |

SW1/7 |

|

27256 |

pins 1 & 2 closed |

Off |

|

27512 |

pins 2 & 3 closed |

On |